More Current Mirrors in Analog Layout

In my previous blog, (Current Mirrors in Analog Layout) I looked at a few techniques for matching MOSFETs in a typical current mirror. In this post, I will look at matching in multiple leg mirrors and the benefits of inserting dummy devices.

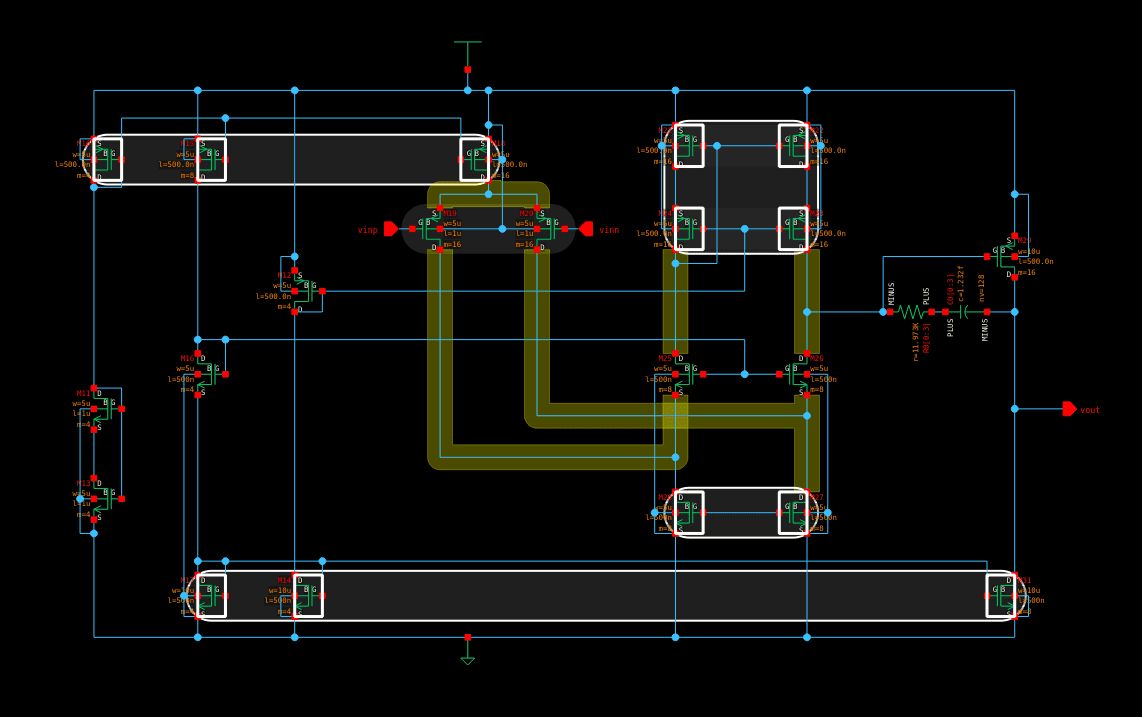

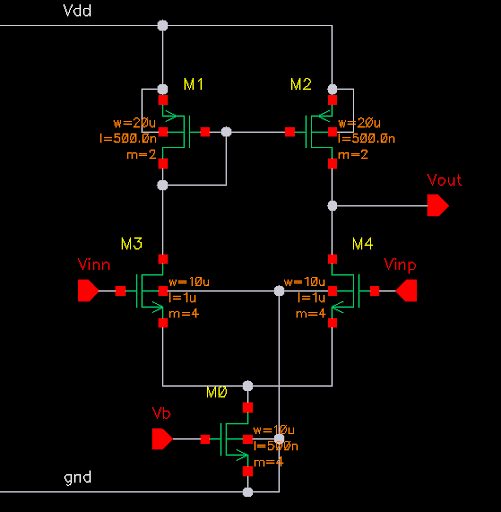

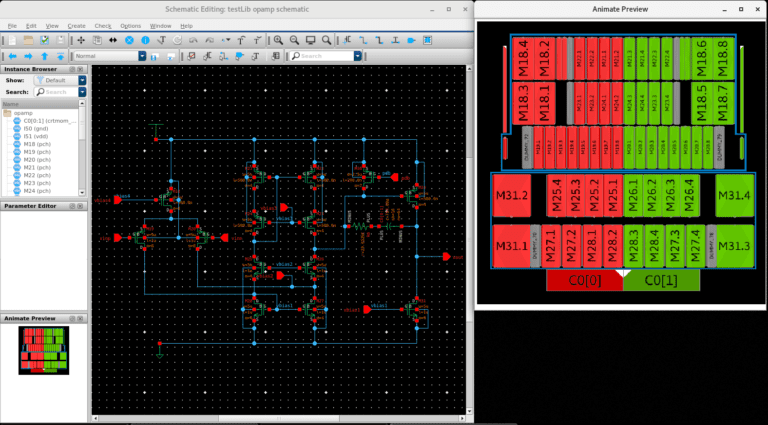

The schematic diagram above is of a typical operational amplifier (opamp), displayed in Pulsic’s Animate Preview design tool. The highlights show various structures in the circuit, as shaded areas around instances and critical nets. I have further selected (white boxes) the current mirrors in this circuit. As discussed previously, current mirrors are a core building block of many practical analog circuits and over 50% of the devices in this circuit are current mirrors.

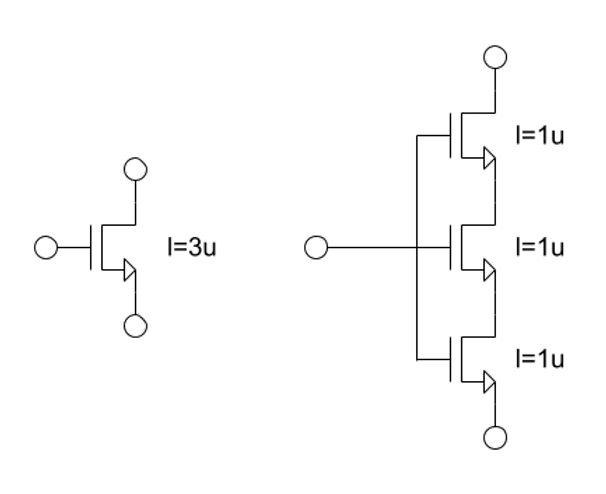

Let’s look in more detail at the layout of a couple of the mirrors in this circuit. The mirror in the top left is the bias generator for the differential pair. The mirror has a gate-drain connected reference device and then connected two bias devices. This type of multi-leg mirror is commonly used in analog circuits, and it not unusual for circuits to contain mirrors with 5 or more legs. The challenge when laying out this circuit is that the designer must now match multiple devices. Additionally, the width of each leg might be different. A current steering DAC circuit is constructed from a multi-leg current mirror with the width of each leg doubling for each bit.

An effective way to match the devices in a multi-leg current mirror is to start by placing the reference device in the center.

The further a device is from the reference the less likely it is to match the reference, process variation is smaller for devices close to each other, with devices further away from the center being less likely to match. Putting the bias in the center evens out the distance to the bias devices.

The bias devices are then typically placed in a common centroid pattern around the central reference device.

This image shows this type of layout with each of the devices highlighted in a different color. The blue devices are the bias for the differential pair.

Placing critical legs closer to the reference device, and other legs further away. Improves matching for the critical legs, again by bringing them closer to the reference device we reduce the process variation. Additionally, the devices near the center of an array of similar devices are less likely to be affected by various LDE and optical issues, further improving matching between them.

An alternative strategy often seen is to place devices with larger m-factor on the outside, allowing smaller devices (which are more susceptible to variation) to be closer to the reference device.

It is also possible to use a maximum dispersion pattern for multi-leg current mirrors. In the next image, you can the central reference device on the left and one of the bias devices selected on the right. This does improve matching between the devices by averaging out the impact of process variation, the downside is that the routing for this type of pattern is considerably more complex.

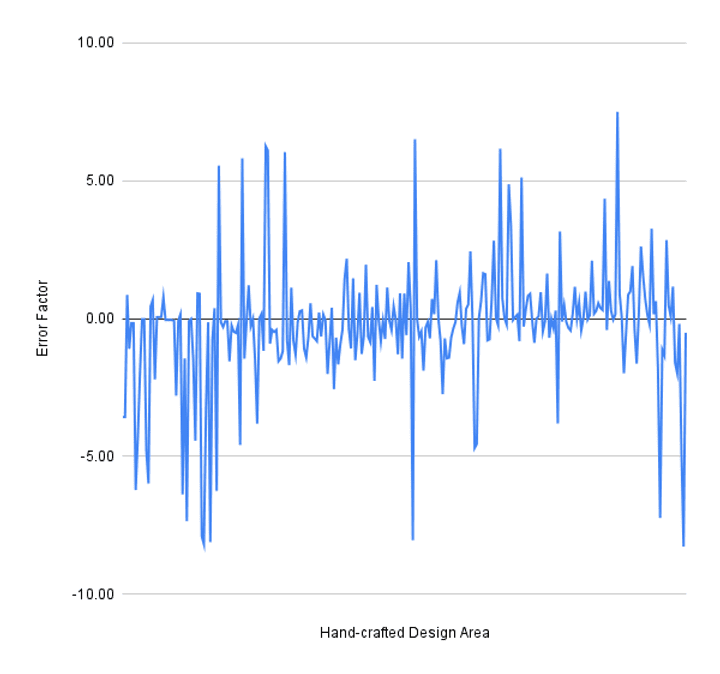

Finally, let’s look at dummy devices and current mirrors. Many processes require designers to use dummies if they need matching devices. Later processes require dummies at the end of each “row” for all devices.

The image above shows a current mirror with a single dummy at the end of each row of devices. These dummies improve matching in two main ways.

The first is that the dummies help ensure that each device in the current mirror has the same geometry when etched in silicon. Optical distortion resulting from sub-wavelength patterning is minimized by repeated patterns in the layout. Process engineers are able to use techniques such as optical process correction (OPC), but uniform patterns are far easier to produce. Where those patterns change, the silicon deviates from the drawn layout the most. By inserting dummies at the end of the current mirror designers extend the pattern, meaning that the matched devices are inside the core of the etched pattern.

The second reason that dummies help matching is by reducing certain types of LDE. Dummies reduce well proximity effect (discussed in the previous article), by increasing the distance of the matched devices from the well edge.

Sometimes it is necessary to add more than one dummy device to each row. It can also be necessary to add additional rows of dummies above and below the current mirror, particularly if the adjacent sections of the circuit have devices with different parameters. Again the aim is to put the critical matching devices in the center of a large area of identically repeating layout.

The complexity of analog layout usually means that engineers and designers have to iterate between circuit and layout fine-tuning parameters and testing different layout strategies. With even a simple circuit each iteration can take many hours to days, often leading to a total design time of weeks.

Pulsic’s Animate Preview uses all the techniques discussed in an intelligent way to create a layout preview of your design in seconds, reducing design layout iterations.

Visit https://animate.pulsic.com to learn how you can use Animate Preview for free, in your analog design flow.